在基于传统半导体材料制造电子设备时,工程师需要完成一个称为掺杂的关键步骤。掺杂本质上需要将杂质引入半导体,以实现对其光学、电学和结构特性的调制。

尽管掺杂是基于半导体的电子产品发展的关键步骤,但许多传统的掺杂策略会引入过多的载流子,将离子化的掺杂剂留在通道中并阻碍电荷载流子的传输。因此,一些工程师一直在尝试设计调制掺杂技术,将离子化掺杂剂与通道分离。

二维半导体中电荷载流子的传输,例如过渡金属二硫属化物(TMDC),可能受到多种内部和外部因素的影响。事实上,在这些材料中,载流子受到环境因素引起的散射效应的高度限制和影响。

由于这种对散射效应的敏感性,迄今为止,二维材料已被证明非常难以研究,研究人员尚未完全了解它们的基本物理特性。为了研究这些材料,特别是研究它们内部发生的量子现象,研究人员应该首先消除不需要的散射效应。

消除散射效应还可以提高基于 2D 半导体的器件的性能,因为过去的研究发现,这些效应会对器件的性能产生不利影响并限制其在实际应用中的潜力。虽然研究人员提出了几种消除外部散射源的策略,但迄今为止,减少二维材料中发生的固有散射已被证明极具挑战性。

高丽大学和韩国其他研究所的研究人员最近推出了一种有助于减少二维半导体材料内在散射效应的策略。在Nature Electronics上发表的一篇论文中提出的这种策略能够通过范德华 (vdW) 能带工程和远程电荷转移掺杂来调制二维半导体中的掺杂。

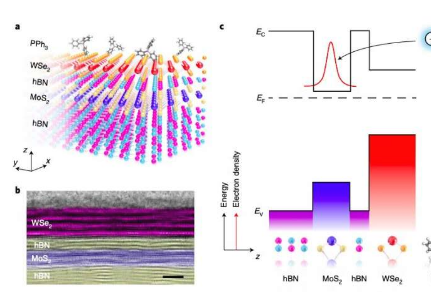

“我们报告了二维晶体管的远程调制掺杂,该晶体管由带调制的二硒化钨/六方氮化硼/二硫化钼异质结构组成,”研究人员在他们的论文中写道。“下面的二硫化钼通道是通过二硒化钨表面掺杂剂的受控电荷转移进行远程掺杂的。”

使用他们的掺杂调制策略,研究人员能够实现一种本征散射减少的晶体管。这显着提高了器件的载流子迁移率(即,电荷载流子通过器件的速度)。

研究人员在他们的论文中解释说:“调制掺杂的器件表现出二维限制的电荷传输和杂质散射的抑制,表现为随着温度降低而增加迁移率。” “我们的二硫化钼调制掺杂场效应晶体管的室温迁移率为 60 cm 2 V –1 s –1;相比之下,直接掺杂的晶体管的迁移率为 35 cm 2 V –1 s –1 .”

未来,这组研究人员进行的研究可以为开发更快、更高效的基于半导体的电子产品铺平道路。事实上,工程师可以使用最近论文中提出的方法来控制 2D 场效应晶体管的载流子迁移率和密度。